Crossing the 10-Transistor Barrier of TCAD Device Simulation跨越 10-晶体管 TCAD 器件仿真壁垒

关于这方面的发展状况可通过此文了解。

一直以来都认为 TCAD 器件仿真器只能够仿真一到两个晶体管。

近年来,TCAD 已经被用来仿真一些小的电路,比如 6 管SRAM,但是对于 TCAD 仿真器的偏颇认识依然存在,认为如果对超过 10 个晶体管,网格节点多于 20,000 的电路进行仿真依然是不太可行的,仿真时间过于漫长,对硬件配置的要求也非常高。

在文章中,我们阐述了珂晶达公司在 TCAD 仿真器开发上的新进展。珂晶达提出了一个克服 10-晶体管壁垒的 TCAD 解决方案,从而把 TCAD 仿真推向了一个新的时代。

为什么仿真大电路会比较困难?

现代 TCAD 仿真器在网格节点数目(或者说晶体管数目)上并没有硬性限制。仿真 10 个或者更多晶体管的障碍,不仅仅是仿真时间太长和硬件配置要求太高,还包括非常容易发生的仿真不收敛问题。

电路规模不断扩大以及由此导致的仿真成本上升

随着电路中晶体管数目的上升,如图 1 所示,TCAD 模型中网格节点数目也随之上升,随之而来的就是 TCAD 仿真需要耗费的时间、以及硬件内存的配置也随之上升。

图 1 珂晶达 Genius 仿真器仿真 CMOS 反相器所需内存随网格节点数目的变化

TCAD 仿真中最昂贵的计算步骤是求解线性方程。就所需要的内存大小来说,对于大规模电路,直接线性求解器是迭代求解器的 5 到 10 倍,而且随着电路规模的扩大和网格节点数目的上升,这个比例还要变大。

就运算时间来说,直接求解器所耗费的时间渐近于 O(n2),n 是网格节点数目;迭代求解器所耗费的时间渐近于O(kn), n 是网格节点数目, k 是所需要的迭代次数。 对于一些较容易的问题,迭代求解器几次迭代就可以收敛,从而仿真时间很短,优势相对于线性求解器很明显;如果是一些困难的问题,迭代求解器需要非常多的迭代次数,这样就可能导致求解速度甚至慢于直接求解器;如果是更极端的问题,迭代求解器可能会收敛失败。

收敛困难

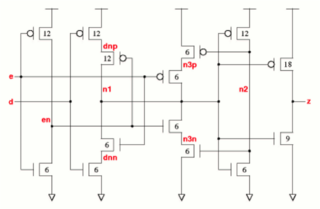

对于较复杂的电路,浮空节点或浮空区域将会出现,而这些浮空节点或浮空区域的电压,是由 2 条或者更多条微弱电流路径之间的相互平衡决定。例如图 2 所示的锁相器电路,总是有 2 个浮空节点(dnp/dnn or n3p/n3n)存在。

图 2 锁相器电路原理图及版图

众所周知,浮空区域在 TCAD 仿真中会带来很大的收敛难度。从技术上来说,浮空区域对线性和非线性(Newton)求解器的性能都有不利影响。 首先,包含有浮空区域的电路系统,将会导致雅克比矩阵的条件数急剧上升到 1020 数量级,迭代线性求解器几乎无法处理这样的状况, 甚至一些高性能直接求解器在一些极端复杂情况下也会求解失败;其次,非线性求解器经常会遇到局部极小和近似平坦的‘谷’,在这种情形下也很难满足特定的收敛准则。

很多 TCAD 用户会采用瞬时分析的方法来求得较好的收敛性,即电压保持恒定,执行瞬时分析直到器件达到稳定状态。 但这种方法通常需要大量的间步,因而仿真速度较慢。

如果选择昂贵的直接线性求解器,以及速度较慢的瞬时分析方法来执行仿真,当网格数目超过100,000 时, 仿真所耗费的时间以及对硬件配置的要求,就会迅速变得不可接受。这些客观上的限制导致 TCAD 用户只能够 针对简单的电路进行仿真,这也就造成了所谓的 10 晶体管壁垒。

Cogenda's Solution珂晶达解决方案

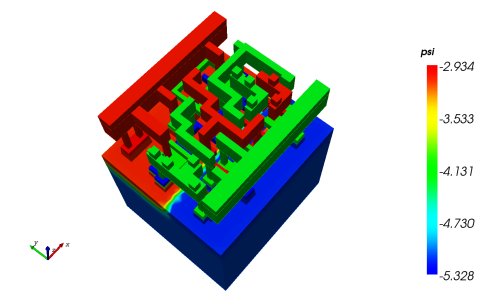

珂晶达提出了一个独有的"伪-时间"算法来解决 TCAD 仿真中遇到的电路规模及收敛性的问题。 图 3 所示为由 14 个晶体管搭建的 CMOS 锁相器电路静电势分布仿真结果, 仿真模型网格节点数目接近300,000,仿真这样的电路是一个史无前例的挑战,一般的 TCAD 器件仿真器根本无法处理。 珂晶达开发的 Genius 器件仿真器可以很顺利的处理这样的大结构、甚至更大结构的问题。

图 3 锁相器电路静电势分布

伪-时间算法是一个瞬时模式(transient-mode),其拥有与瞬时分析方法(transient analyses)相同的易收敛特性。 另外,伪-时间算法不使用物理时间,其使用伪时间步,从而可以通过更优化的方法让器件达到稳定状态。

图 4 显示了伪-时间算法和标准稳态算法性能的比较,经典算法(目前用于所有的 TCAD 软件)有收敛性的问题, 而且直接求解器(非常耗内存)也非常慢。迭代求解器在仿真伊始即执行伪-时间算法,具有收敛性好、节省大量内存、速度更快的特点。 在珂晶达发布的 1.7.2-3 版 Genius 软件中,包含了一个优化的伪-时间算法,仿真时间可以进一步减少。

图 4 不同算法下耗费时间和内存配置要求的比较 (器件为6管 SRAM ,机器为 8 核工作站)

伪-时间算法可以极大地提高 Genius 仿真器的性能,但这并非珂晶达唯一的技术。除了伪-时间算法,珂晶达还开发了许多高效率和可扩展性的产品。 考虑到一个看起来无足轻重的小模块都可能成为瓶颈从而影响整体的性能,Genius 的每一个组件都采用了并行计算的设计和优化方法。

结论

通过数年全面的研究和开发,珂晶达 Genius 已经成功跨越了10-晶体管壁垒。 因此,利用不太昂贵的硬件配置,对超过 20 个晶体管,多达 600,000 个网格节点的电路进行仿真, 并在可以接受的时间周期内得到结果,已经变得非常可行。